A „Hiddenite” nevű új gyorsítóchip, amely a legkorszerűbb eredményeket tudja elérni pontosság a ritka „rejtett neurális hálózatok” kiszámításánál kisebb számítási terhelés mellett most a Tokyo Tech kutatói fejlesztették ki. A javasolt on-chip modellkonstrukció alkalmazásával, amely a súlygenerálás és a „szupermaszk” bővítés kombinációja, a Hiddenite chip drasztikusan csökkenti a külső memória hozzáférését a nagyobb számítási hatékonyság érdekében.

A mély neurális hálózatok (DNN-ek) az AI (mesterséges tanulás) gépi tanulási architektúrájának összetett részei, amelyek számos paramétert igényelnek a kimenetek előrejelzésének megtanulásához. A DNN-ek azonban „levághatók”, ezáltal csökkenthető a számítási terhelés és a modell mérete. Néhány évvel ezelőtt a „sorsjegy-hipotézis” záporozta a gépi tanulás világát. A hipotézis azt állította, hogy egy véletlenszerűen inicializált DNN olyan alhálózatokat tartalmaz, amelyek betanítás után az eredeti DNN-nek megfelelő pontosságot érnek el. Minél nagyobb a hálózat, annál több a „sorsjegy” a sikeres optimalizáláshoz. Ezek a sorsjegyek így lehetővé teszik a „csonkított” ritka neurális hálózatok számára, hogy a bonyolultabb, „sűrűbb” hálózatokkal egyenértékű pontosságot érjenek el, ezáltal csökkentve az általános számítási terheket és az energiafogyasztást.

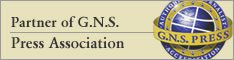

1. ábra: A HNN-ek ritka alhálózatokat találnak, amelyek az eredeti sűrű betanított modellel egyenértékű pontosságot érnek el. Köszönetnyilvánítás: Masato Motomura a Tokyo Techtől

Az ilyen alhálózatok megtalálásának egyik módja a rejtett neurális hálózat (HNN) algoritmus, amely ÉS logikát (ahol a kimenet csak akkor magas, ha az összes bemenet magas) használ az inicializált véletlenszerű súlyokon és egy „bináris maszkot”, amelyet „supermaszknak” neveznek. (1. ábra). A felső-k% legmagasabb pontszámmal meghatározott szupermaszk a nem kiválasztott és a kiválasztott kapcsolatokat 0-val, illetve 1-gyel jelöli. A HNN segít csökkenteni a számítási hatékonyságot szoftver oldalról. A neurális hálózatok számítása azonban a hardverkomponensek fejlesztését is igényli.

A hagyományos DNN-gyorsítók nagy teljesítményt kínálnak, de nem veszik figyelembe a külső memória-elérés okozta energiafogyasztást. A Tokiói Technológiai Intézet (Tokyo Tech) kutatói Jaehoon Yu és Masato Motomura professzorok vezetésével új „Hiddenite” nevű gyorsítóchipet fejlesztettek ki, amely drasztikusan megnövelt energiafogyasztás mellett képes kiszámítani a rejtett neurális hálózatokat. „A külső memóriához való hozzáférés csökkentése a kulcsa az energiafogyasztás csökkentésének. Jelenleg a nagy következtetési pontosság eléréséhez nagy modellekre van szükség. Ez azonban növeli a külső memória hozzáférését a modell paramétereinek betöltéséhez. A Hiddenite fejlesztésének fő motivációja az volt, hogy csökkentsük ezt a külső memória-hozzáférést” – magyarázza Prof. Motomura. Tanulmányuk a közeljövőben szerepel majd Nemzetközi Szilárdtest-áramköri Konferencia (ISSCC) 2022, egy rangos nemzetközi konferencia, amely bemutatja az integrált áramkörök terén elért csúcsokat.

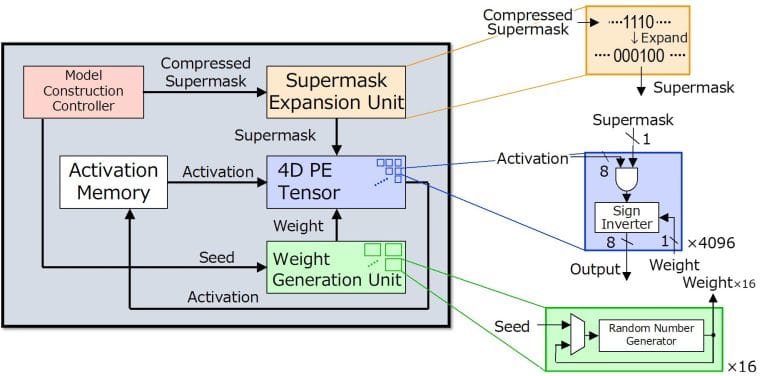

2. ábra. Az új Hiddenite chip chipen belüli súlygenerálást és chipen belüli „szupermaszk-bővítést” kínál, hogy csökkentse a külső memória-hozzáférést a modellparaméterek betöltéséhez. Köszönetnyilvánítás: Masato Motomura a Tokyo Techtől

A „Hiddenite” a Hidden Neural Network Inference Tensor Engine rövidítése, és az első HNN következtetési chip. A Hiddenite architektúra (2. ábra) háromszoros előnyt kínál a külső memória-hozzáférés csökkentése és a magas energiahatékonyság elérése érdekében. Az első az, hogy a chipen belüli súlygenerálást kínál a súlyok újragenerálásához véletlenszám-generátor használatával. Ezzel szükségtelenné válik a külső memória elérése és a súlyok tárolása. A második előny az „on-chip szupermaszk bővítés”, amely csökkenti a gyorsító által betöltendő szupermaszkok számát. A Hiddenite chip által kínált harmadik fejlesztés a nagy sűrűségű négydimenziós (4D) párhuzamos processzor, amely maximalizálja az adatok újrafelhasználását a számítási folyamat során, ezáltal javítva a hatékonyságot.

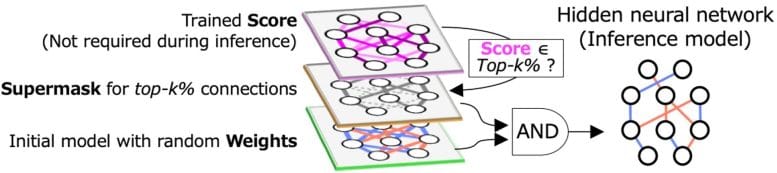

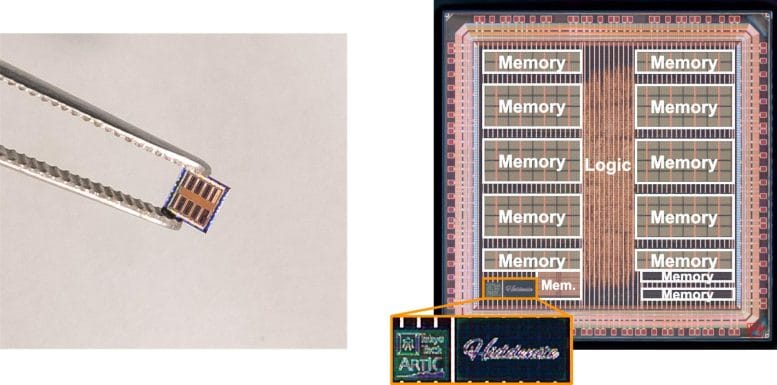

3. ábra: 40 nm-es technológiával készült, a chip területének magja mindössze 4.36 négyzetmilliméter. Köszönetnyilvánítás: Masato Motomura a Tokyo Techtől

„Az első két tényező különbözteti meg a Hiddenite chipet a meglévő DNN-következtetés-gyorsítóktól” – tárja fel Motomura professzor. „Sőt, bevezettünk egy új oktatási módszert a rejtett neurális hálózatokhoz, az úgynevezett „pontszámdesztillációt”, amelyben a hagyományos tudáslepárlási súlyokat a pontszámokba desztilláljuk, mivel a rejtett neurális hálózatok soha nem frissítik a súlyokat. A pontszámdesztilláció pontossága a bináris modelléhoz hasonlítható, miközben fele akkora, mint a bináris modell.”

A Hidite architektúra alapján a csapat egy prototípus chipet tervezett, gyártott és mért a Taiwan Semiconductor Manufacturing Company (TSMC) 40 nm-es eljárásával (3. ábra). A chip mindössze 3 mm x 3 mm, és egyszerre 4,096 MAC (multiply-and-accumulate) műveletet kezel. A számítási hatékonyság legkorszerűbb szintjét éri el, akár 34.8 billió vagy tera műveletet másodpercenként (TOPS) watt teljesítményenként, miközben a modellátvitel mennyiségét a felére csökkenti, mint a binarizált hálózatok esetében.

Ezek az eredmények és a valódi szilícium chipben való sikeres bemutatásuk minden bizonnyal újabb paradigmaváltást idéz elő a gépi tanulás világában, megnyitva az utat a gyorsabb, hatékonyabb és végső soron környezetbarátabb számítástechnika felé.